# 15V 駆動の微細 IGBT における電流飽和メカニズムの研究

伊倉 巧裕\* 小野澤 勇一(富士電機) 中川 明夫(中川コンサルティング事務所)

Study on Current Saturation Mechanism of Miniaturized IGBTs Driven by 15V Gate Voltage Yoshihiro Ikura\*, Yuichi Onozawa, (Fuji Electric Co, Ltd.) Akio Nakagawa, (Nakagawa Consulting Office, LLC.)

In this work, we report detailed current saturation mechanism of the miniaturized IGBTs and shows solutions to keep the saturation current sufficiently low, even if 15V gate voltage is used. There are two saturation mechanisms which result in two inflection points of the current saturation characteristics of the miniaturized IGBTs. Based on our findings, there are two ways to suppress the saturation current increase. One is decreasing the lateral P-base resistance under the N+-Emitter. The other is decreasing the hole current density.

**キーワード**: IGBT, 微細化, スケーリング, 飽和電流, 短絡耐量 (IGBT, miniaturization, scaling, saturation current, short circuit ruggedness)

#### 1. 背景

IGBT の特性を改善するため表面構造のセルピッチの微細化、あるいは構成要素を均等に縮小するスケーリングが進められている(文献1、2)。トレンチで挟まれたメサ部の幅を狭くすることで、IE効果が高まりオン電圧を下げることができる。しかしながら、ゲート電圧15Vでの駆動のまま微細化すると、飽和電流が増加し短絡耐量が低下するという問題がある。文献2で提案されているスケーリングでは、ゲート電圧5Vで駆動することで飽和電流を低下できることが報告されている。しかし、ゲート駆動電圧を下げることはノイズに対する耐性という観点からは得策ではない。

本報告では、微細 IGBT の飽和電流特性において電流が 飽和するメカニズムの詳細を明らかにし、ゲート電圧15V での駆動でも飽和電流の増加を抑制するための方法を報告 する。

#### 2. デバイス構造と飽和電流特性

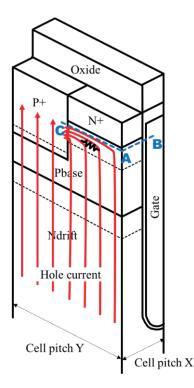

検討したデバイス構造のゲート電極はトレンチ形状と し、表面の N+エミッタ層と P+層がトレンチに対して直 交する構造とした。また、微細化するときにはトレンチ幅 を調整してトレンチピッチを固定した。

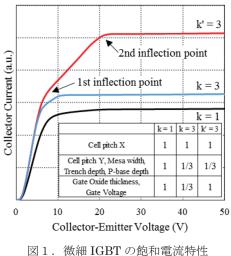

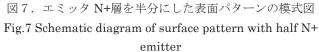

図1に Synopsys 社の TCAD シミュレーションを用いて 計算した飽和電流特性を示す。ゲート駆動電圧 15V の標準 的な構造(図中の k=1)の特性はコレクタ電圧が 8V 程度で 飽和し比較的低い電流で一定となる。これに対し、文献2 にあるスケーリング則にのっとり、ゲート酸化膜の厚さを 含めた表面構造の構成要素の寸法を1/3にし、ゲート駆動電 圧を1/3にした場合(図中のk=3)も低い飽和電流となる。 ところが、ゲート酸化膜とゲート駆動電圧を元のまま変え ず、他の構成要素の寸法を1/3にした場合(図中のk'=3)、 飽和電流が大きく増加する。

# 3. 電流が飽和するメカニズムの考察

k'=3 の飽和電流特性には2つの変曲点がある。それぞれ の変曲点および変曲点で区切られたコレクタ電圧 Vce の区 間において、どのような現象が起きてコレクタ電圧 Vce に 対するコレクタ電流 Ic の傾きが変化しているかを考察し た。

# a) <u>Vce=0V</u>から変曲点1の区間

Vce に対する Ic の傾きが最も高い区間。Vce が高くなる につれ電子速度が速くなりチャネルの電子電流が増加す る。またそれに伴って裏面からホールが注入されホール電 流の成分も増加する。

#### b) <u>変曲点1</u>

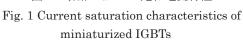

Vceが7~8Vより高くなると傾きが緩やかになる。これは 電界に対する電子速度の増加が飽和するためであると考え られる。図2にチャネルにおける不純物濃度とVceが増加 するにつれて変化する電界強度と電子速度を示す。Vceが増 加するにつれて電界強度は一様に増加する一方、電子速度 はVceが8Vまでは増加するが、Vceが8V以上ではそれ以 上増加しなくなる。

# 図2. チャネルにおける不純物濃度、電界強度と電子速度 Fig. 2 Doping concentration, Electric field and Electron velocity at the channel

# c) <u>変曲点1から変曲点2の区間</u>

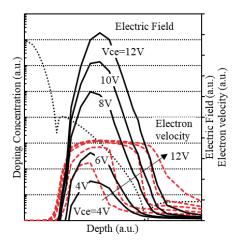

Vce に対する Ic の傾きは緩やかになるが線形に増加する 区間。チャネル電流の増加は飽和するが、図3の模式図の ようにホール電流が N+エミッタ層の下の P ベース層を通 過するときに P ベース層が寄生抵抗として働き、P ベース 層の中央部の電位が持ち上がるためチャネル以外を通る電 流が流れており、Vce が増加するに伴って P ベース層が空 乏化し寄生抵抗が増加するため、チャネル以外の電子電流 も増加すると推定される。

図3. デバイス表面構造とホール電流のイメージ図 Fig.3 Surface structure and hole current stream line

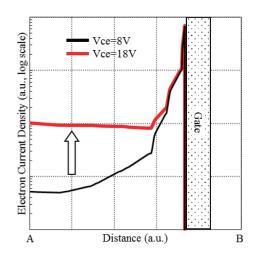

図4に変曲点1(Vce=8V)と変曲点2の直前(Vce=18V) のときの図3中のカットラインA-Bにおける電子電流密度 を示す。ゲート酸化膜に接したチャネルの電子電流密度は ほぼ変わっていないが、チャネル以外のPベース層を流れ る電子電流密度が増加している。

図4.変曲点1 (Vce=8V) と変曲点2の直前 (Vce=18V) のときのカットライン A-B における電子電流密度 Fig. 4 Electron current density along cutline A-B at Vce=8V and 18V

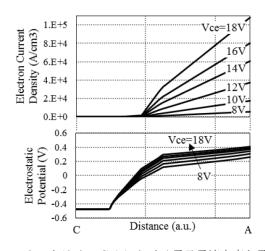

図5に Vce が8Vから18Vに増加するにつれて変化する カットライン C-Aにおける電子電流密度と電位を示す。Vce が増加するにつれて、エミッタに接続された P+層から最も 離れた点Aの電位が増加し、それに伴って電子電流密度が 増加している。

#### d) 変曲点2より高い Vce の区間

Vce が 22V より高くなるとコレクタ電流は完全に飽和す る。Vce がゲートトレンチの電位よりも高くなると、ゲート トレンチで挟まれたメサ領域の電位がそれ以上高くならな いため電流が完全に飽和する。

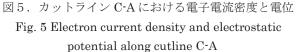

図6にメサ中央部の不純物濃度と電位を示す。Vceが増加 するにつれて電位は増加していくが、Vceが22V以上では 点線で示したトレンチ底部の電位はゲート電圧と同じ15V となり、それ以上にほぼ増加しなくなる。

Fig. 6 Doping concentration and electric field at center of mesa region

#### 4. 飽和電流を抑制する方法の検討

これまでの考察で明らかになったように飽和電流を抑制 するためには、変曲点1と変曲点2の間で飽和電流を増加 させないことが重要であると考えられる。

変曲点1と2の間で飽和電流が増加するメカニズムは、 寄生抵抗をホール電流が通過することで電位が持ち上がる ためであるので、次の2つのアプローチが考えられる。

- ① 寄生抵抗を小さくする。

- ホール電流を小さくする。

これらの仮説を検証した結果を次に紹介する。

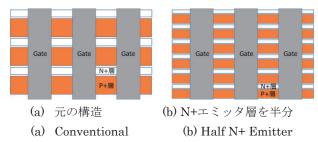

# A) <u>N+エミッタ層の幅を狭くしてN+エミッタ層下のPベ</u> <u>-</u>ス層の寄生抵抗を低下する

N+エミッタ層の幅を短くするとPベース層の寄生抵抗 を小さくできる。例えば、図7に示すように k'=3の構造の N+エミッタ層の幅を、チャネル幅の総和を一定にしたま ま、半分にすることでオン電圧を低く保ったまま飽和電流 の増加を抑制できる。(図8の k"=3)

流特性

Fig. 8 Current saturation characteristics of conventional and proposed miniaturized IGBTs

B) <u>P ベース層の不純物濃度分布を平坦にして N+エミッ</u>

# タ層下の P ベース層の寄生抵抗を低下する

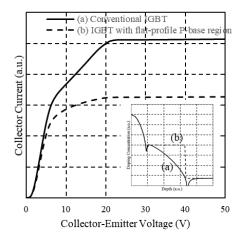

Vce が増加するにつれてPベース層は空乏化するので寄 生抵抗は増加する。これを抑制するために、例えばPベー ス層の不純物濃度分布を平坦にすることで空乏化が抑制さ れ、Pベース層の寄生抵抗を小さくでき、飽和電流の増加 を抑制できる。(図9)

図9. Pベース層の不純物濃度分布を平坦にした微細 IGBT の飽和電流特性

# Fig. 9 Current saturation characteristics of IGBT with flat-profile P-base region

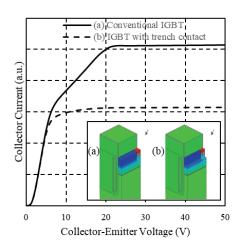

C) トレンチコンタクトを配置してホール電流を低下する N+エミッタ層の中央にトレンチ形状のコンタクトを配置すると N+エミッタ層下の P ベース層を介して流れるホ ール電流を少なくできるので飽和電流の増加を抑制できる (図10)。

図10.トレンチコンタクトを配置した微細 IGBT の飽 和電流特性

Fig. 10 Current saturation characteristics of IGBT with trench contact

#### 5. まとめ

本稿では微細 IGBT の飽和電流特性がどのようなメカニ ズムで形作られるかを明らかにし、ゲート駆動電圧が 15V でも飽和電流の増加を抑制する方法を提案した。

飽和電流特性には2つの変曲点があり、2つの変曲点の 間で電流が増加する原因は、N+エミッタ層の下のPベース 層をホール電流が流れることで、寄生抵抗を構成する Pベ ース層の電位が持ち上がりチャネル以外の電流が増加する ためである。

この電流の増加を抑制するためには、N+エミッタ層の幅 を短くしたり、Pベース層の不純物濃度分布を工夫したりす ることで寄生抵抗を小さくすること、ならびにホール電流 を小さくするためにトレンチコンタクトを配置することが 有効であることを示した。

# 献

文

- A. Nakagawa, "Theoretical Investigation of Silicon Limit Characteristics of IGBT," ISPSD 2006, pp. 5-8, 2006.

- (2) M. Tanaka and I. Omura, "Scaling Rule for Very Shallow Trench IGBT toward CMOS Process Compatibility," ISPSD 2012, pp. 177-180, 2012.

- (3) K. Eikyu, A. Sakai, H. Matsuura, Y. Nakazawa, Y. Akiyama, Y. Yamaguchi and M. Inuishi, "On the Scaling Limit of the Si-IGBTs with Very Narrow Mesa Structure", ISPSD 2016, pp. 211-214, 2016.

- (4) K. Eikyu, A. Sakai, H. Matsuura, Y. Nakazawa, Y. Akiyama and Y. Yamaguchi, "Study on the improved short-circuit behavior of narrow mesa Si-IGBTs with emitter connected trenches", ISPSD 2018, pp. 495-498, 2018.

- (5) M. Tanaka and A. Nakagawa, "Novel 3D narrow mesa IGBT suppressing CIBL", ISPSD 2018, pp. 124-127, 2018.